- 您现在的位置:买卖IC网 > Sheet目录1991 > CS5342-CZZ (Cirrus Logic Inc)IC ADC AUD 105DB 200KHZ 16-TSSOP

16

DS608F1

CS5342

4.2.3

Master Clock

The CS5342 requires a Master clock (MCLK) which runs the internal sampling circuits and digital filters.

There is also an internal MCLK divider which is automatically activated according to the frequency of the

MCLK. Table 3 shows a listing of the external MCLK/LRCK ratios that are required. Table 3 lists some

common audio output sample rates and the required MCLK frequency. Please note that not all of the listed

sample rates are supported when operating with a fast MCLK (768x, 384x, 192x for Single-, Double-, and

Quad-Speed Modes, respectively).

4.3

Serial Audio Interface

The CS5342 supports both IS and Left-Justified serial audio formats. Upon start-up, the CS5342 will detect

the logic level on SDOUT (pin 4). A 10 k

pull-up resistor to VL is needed to select IS format, and a 10 k

pull-down resistor to GND is needed to select Left-Justified format. Please see Figures 13 through 16 for

more information on the required timing for the two serial audio interface formats.

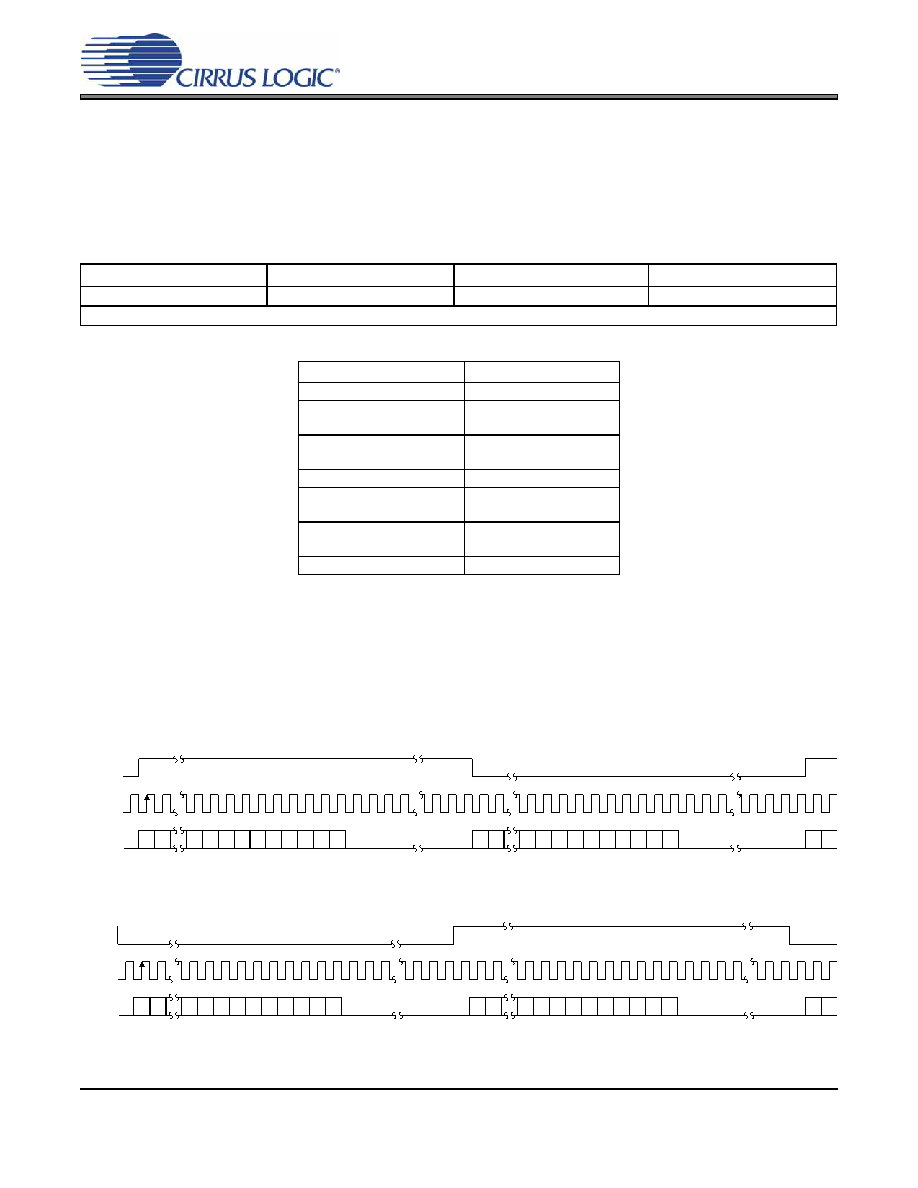

Single-Speed Mode

Double-Speed Mode

Quad-Speed Mode

MCLK/LRCK Ratio

384x, 768x

192x, 384x

96x*, 192x

* Quad-Speed, 96x only available in Master Mode.

SAMPLE RATE (kHz)

MCLK (MHz)

32

12.288

44.1

16.9344

33.8688

48

18.432

36.864

64

12.288

88.2

16.9344

33.8688

96

18.432

36.864

192

36.864

Table 3. Master Clock (MCLK) Frequencies for Standard Audio Sample Rates

Figure 19. Left-Justified Serial Audio Interface

SDATA

23 22

7

6

23 22

SCLK

LRCK

23 22

54

32

10

8

76

54

32

10

8

9

Left Channel

Right Channel

Figure 20. IS Serial Audio Interface

SDATA

23 22

8

7

23 22

SCLK

LRCK

23 22

65

43

21

0

87

65

43

21

0

9

Left Channel

Right Channel

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CS5345-CQZ

IC ADC AUD 104DB 200KHZ 48-LQFP

CS5345-DQZ

IC ADC AUD 104DB 200KHZ 48-LQFP

CS5346-CQZR

IC ADC AUD 103DB 200KHZ 48-LQFP

CS5351-BZZ

IC ADC AUD 108DB 204KHZ 24-TSSOP

CS5361-DZZ

IC ADC AUD 114DB 204KHZ 24-TSSOP

CS5364-CQZR

IC ADC 4CH 114DB 216KHZ 48-LQFP

CS5366-DQZR

IC ADC 6CH 114DB 216KHZ 48-LQFP

CS5368-DQZ

IC ADC 8CH 114DB 216KHZ 48-LQFP

相关代理商/技术参数

CS5342-CZZR

功能描述:音频模/数转换器 IC IC 105dB 192 kHz Multi-bit Audio ADC RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装:

CS5342-DZZ

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:105 dB, 192 kHz, MULTI-BIT AUDIO A/D CONVERTER

CS5343

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:98 dB, 96 kHz, Multi-Bit Audio A/D Converter

CS5343_07

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:98 dB, 96 kHz, Multi-Bit Audio A/D Converter

CS5343_08

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:98 dB, 96 kHz, Multi-Bit Audio A/D Converter

CS5343-CZZ

功能描述:音频模/数转换器 IC 98dB 24-Bit 96kHz Stereo ADC RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装:

CS5343-CZZR

功能描述:音频模/数转换器 IC IC 98dB 24-bit 96kHz Stereo ADC RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装:

CS5343-DZZ

功能描述:音频模/数转换器 IC 98dB 24-Bit 96kHz Stereo ADC RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装: